- Vẽ mạch:

Bộ đếm này sử dụng flip –flop D nối tiếp. Các ngõ vào T (hoặc J = K) của ba flip-flop đều được nối lên nguồn + Vcc.

Xung cần đếm được đưa vào ngõ ck (clock) của flip – flop đầu tiên.

- Giải thích nguyên lí:

Ban đầu, tất cả các flip – flop đều ở trạng thái 0 (Q0 = Q1 = Q2 = 0). Khi xung đồng hồ xuống (falling edge) đầu tiên đến, flip – flop đầu tiên (Q0) lật trạng thái, tức là Q0 = 1. Sau mỗi xung đồng hồ, Q0 lại lật trạng thái một lần nữa (Q0 = 0). Do Q0 lại trở thành ngõ vào xung đếm của flip – flop thứ hai (Q1), tần số ngõ ra Q1 bằng một nửa tần số ngõ vào Q0.

Tương tự, tần số ngõ ra Q2 bằng một nửa tần số ngõ vào Q1.

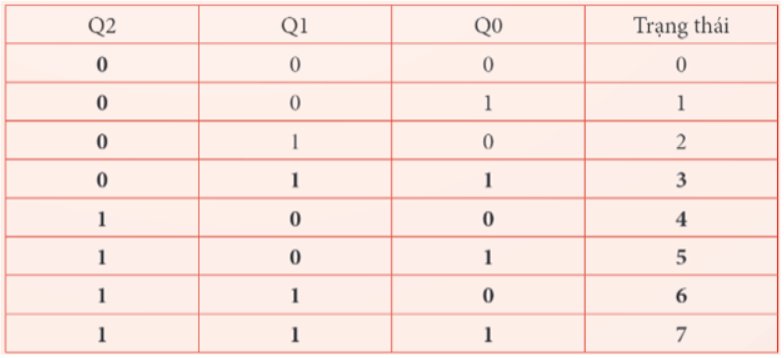

- Bảng chân lí:

Đúng 0

Bình luận (0)